Maintaining signal integrity (SI) and preventing connector damage for high-speed signals requires careful attention to design details such as impedance matching, minimizing reflection, reducing crosstalk, and ensuring correct termination. This begins with defining specific signal speed and bandwidth requirements and choosing the best connector. The definition of high-speed signals is relative to the application, and over time, in many cases it is constantly increasing. For instance, in today's digital electronic applications, high-speed signals are defined as ≥10 Gbps. In some applications, the dividing line is moving towards 100 Gbps or higher.

What is the most suitable connector for high speed?

The identification of the best high-speed connector depends on application factors, such as the working environment, required bandwidth, installation requirements, etc. Many connectors are designed to meet specific industry standards. Some standard connectors include (Figure 1) : Optical fiber transmission offers the highest speed, usually > It has 1 picobit per second and a strong ability to resist electromagnetic interference (EMI). Two examples among the numerous options include high-speed LC connectors for high-density networks and MPO connectors for high-bandwidth data center installations. The backplane gives priority to low insertion loss and high signal integrity (SI). For example, Amphenol's Paladin HD and EXAMAX2, TE Connectivity's IMPACT, MULTIGIG RT and Samtec's ExaMAX. The relay connector is a board-to-board dedicated interconnection specifically designed for stacked parallel PCBS in high-density, high-performance applications. Some options include Samtec's SEARAY™, Molex's HD Mezz and TE Connectivity's Mezalok. There are various industry standards for RF/coaxial connectors, such as SMA, SMPM and BNC, which are specifically optimized for millimeter-wave systems and RF testing.

The selection, integration and system testing of high-speed signal connectors focus on optimizing signal integrity. Optimal signal integrity is crucial for maintaining data quality and timing. The key signal integrity indicators of high-speed signals include eye diagram indicators (height, width, jitter), S-parameters (also known as scattering parameters) such as insertion loss and return loss, as well as impedance control. For instance, matching the differential impedance of the connector (typically 100 Ω or 85 Ω) with the system helps minimize insertion loss and crosstalk, and ensures sufficient bandwidth. The differential impedance of a connector measures the degree of damage to a pair of high-speed electrical signals transmitted through the connector pins/contacts driven by an equal-amplitude, inverse signal. For high-speed systems such as USB, HDMI and PCIe, optimization is the key to preventing signal reflection, which is achieved by matching the impedance of PCB traces. The accuracy of matching can have a certain degree of flexibility.

PCIe example

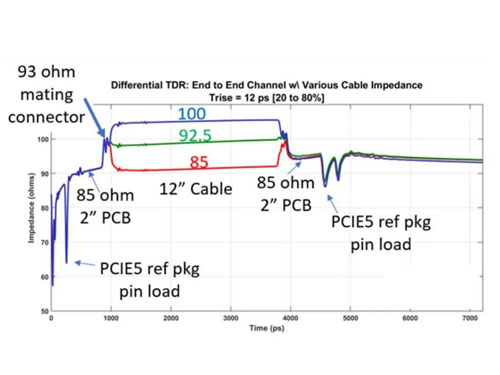

Differential impedance is just one factor that needs to be considered. Figure 2 is a time-domain reflectometer (TDR) diagram of a differential channel. It plots the impedance of the signal over time when it is transmitted between PCBS using a matching connector and a 12-inch cable, demonstrating how different channel impetubers (85 Ω, 92.5 Ω, and 100 Ω) affect signal integrity within the PCIe 5.0 reference system.

This test uses a signal rise time of 12 picoseconds. The test setup includes a 2-inch PCB section and a 12-inch cable, as well as a 93 Ω mating connector. Three different total channel impedances are shown: 85 Ω (red line), 92.5 Ω (green line), and 100 Ω (blue line). This figure shows the influence of impedance matching and signal reflection at different channel points. The selection of cable impedance depends on the priorities of the specific design. For instance, if insertion loss is the most important consideration, then a 93 Ω or 100 Ω cable might be the best choice.

Focus on performance

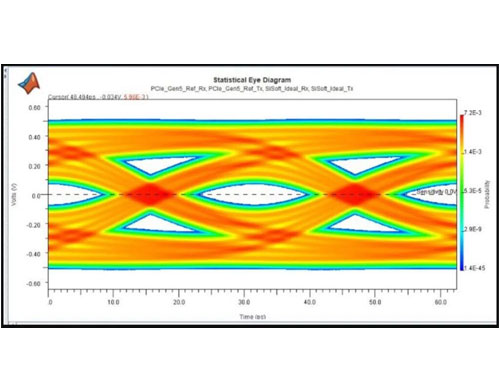

Designers use eye diagrams to visualize the performance of high-speed interconnects. The eye diagram shows how to simulate or measure the distortion of high-speed signals caused by inter-symbol interference (ISI), jitter and noise by simulating or measuring the channel impulse response obtained from S-parameters. The obtained eye diagram shows the cumulative effect of insertion loss (vertical closed eye diagram) and jitter (horizontal closed eye diagram). Common uses of eye diagrams include verifying signal quality and confirming standard compliance. S-parameters, such as S21 for insertion loss and S11 for return loss, are used to describe the frequency response of the channel. Eye diagrams can be measured and analyzed using a sampling oscilloscope or a high-bandwidth real-time digital oscilloscope. The design simulation tool can convert the S-parameter to the time domain through the inverse Fast Fourier Transform (IFFT) to determine the distortion of the digital pulse (Figure 3).